#### 3-1. GENERAL

This section contains information needed to understand the operation of the MITS Altair 8800b computer (8800b). It contains a basic description of the logic symbols used in the 8800b schematics and detailed theory of the 8800b Central Processing Unit. Interface and Front Panel circuits.

#### 3-2. LOGIC CIRCUITS

The logic circuits used in the 8800b drawings are presented as a tabular listing in Table 3-1. The table is constructed to present the functional name, symbolic representation, and a brief description of each logic circuit. Where applicable, a truth table is provided to aid in understanding circuit operation. Although Table 3-1 does not include every logic circuit used in the drawings, all unmentioned circuits (and their symbolic representations) are variations of the circuits presented with their functional descriptions basically the same. The active state of the inputs and outputs of the logic circuits is graphically displayed by small circles. A small circle, at an input to a logic circuit, indicates that the input is an active LOW; that is, a LOW signal will enable the input. A small circle, at the output of a logic circuit, indicates that the output is an active LOW; that is, the output is low in the actuated state. Conversely, the absence of a small circle indicates that the input or output is active HIGH.

Table 3-1. Symbol Definitions

| NAME                        | LOGIC<br>SYMBOL                  | DESCRIPTION                                                                                                                                                                                       |

|-----------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAND gate                   | Y = AB N                         | The NAND gate performs one of the fundamental logic functions.  All of the inputs have to be enabled (HIGH) to produce the desired (LGW) output. The output is HIGH if any of the inputs are LOW. |

| NOR gate                    | $Y = \overline{A + B \dots + N}$ | The NOR gate performs one of the fundamental logic functions.  Any of the inputs need to be enabled (HIGH) to produce the desired (LOW) output. The output is HIGH if all of the inputs are LOW.  |

| Inverter                    | A — Ā                            | The inverter is a device whose output is the opposite state of the input.                                                                                                                         |

| Non-Inverting<br>Bus Driver | AA                               | The non-inverting bus driver is a device whose output is the same state as the input. Data is enabled through the device by applying a (LOW) signal to the E input.                               |

| Inverting<br>Bus Driver     | A — Ā                            | The inverting bus driver is a device whose output is the opposite state of the input. Data is enabled through the driver by applying a (LOW) signal to the E input.                               |

Table 3-1. Symbol Definitions - Continued

| NAME                            | LOGIC<br>SYMBOL                          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Edge triggered D type flip-flop | Truth Table  Tn Tn+1  D Q Q  L L H H H L | Applying a LOW signal to the preset input (P) sets the flip-flop with output Q HIGH and output $\overline{Q}$ LOW. Applying a LOW signal to the clear input (C) resets the flip-flop with Q LOW and $\overline{Q}$ HIGH. This method of setting and resetting the flip-flop is independent of the clock (asynchronous). If a signal is applied to the D input, the flip-flop Q output is directly affected on the positive edge of the clock (truth table). |

| QUAD D flip-flop                | 9                                        | The information on the D inputs is stored during the positive edge of the clock (CK). The clear (C) input, when LOW, resets all flip-flops independent of the clock or D inputs.                                                                                                                                                                                                                                                                            |

| 4-Bit Binary Ripple<br>Counter  | 1                                        | The 4-bit binary ripple counter operation requires that the QA output be externally connected to input CP <sub>B</sub> .  The input count pulses (negative edge) are applied to input CP <sub>A</sub> enabling a divide by 2, 4, 8, and 16 at the QA, QB, QC, and QD outputs. The reset (RO) input resets the counter regardless of the clock input (CP <sub>A</sub> ) when both inputs are HIGH.                                                           |

Table 3-1. Symbol Definitions - Continued

| NAME                     | LOGIC<br>SYMBOL                                                                                                                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12-Bit Binary<br>Counter | 10 — Q <sub>T</sub> — Q <sub>12</sub> MR Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q                                                     | The 12-bit counter is triggered on the negative edge of the clock input (CP). A HIGH on the master reset input (MR) clears all counter stages and forces all outputs (QO-Q11) LOW which is independent of the clock input.                                                                                                                                                                                           |

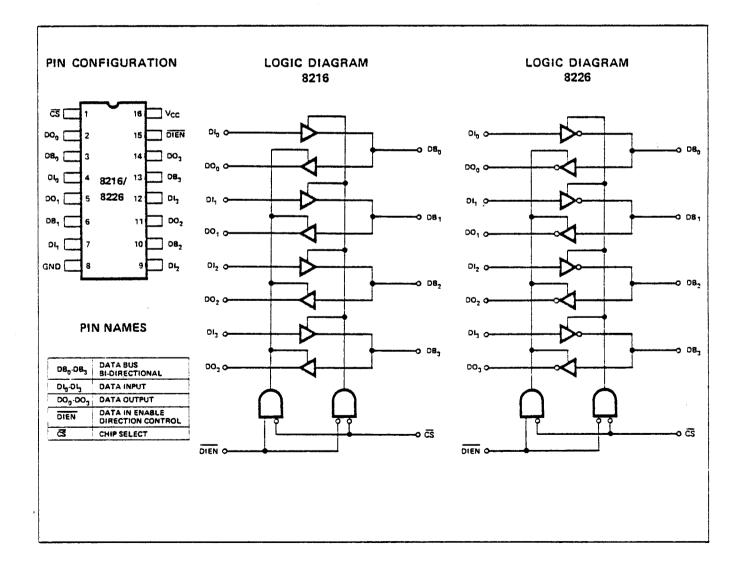

| Bi-Directional<br>Device | 15 DB <sub>0</sub> DB <sub>1</sub> DB <sub>2</sub> DB <sub>3</sub> DB <sub>0</sub> DB <sub>1</sub> DB <sub>2</sub> DB <sub>3</sub> | Output data from a device is present on the $DI_0$ - $DI_3$ lines and is enabled when $\overline{DIEN}$ and $\overline{CS}$ are LOW. Lines $DB_0$ - $DB_3$ transfer the data to the receiving unit. Input data to the device is present on the $DB_0$ - $DB_3$ lines and is enabled when $\overline{DIEN}$ is HIGH and $\overline{CS}$ is LOW. Input data is transferred to the device on the $D0_0$ - $D0_3$ lines. |

| Clock Generator          | 2 — RESIN RESET — 1 3 — RDYIN READY — 4 5 — SYNC STSTB — 7 14 — XTAL 2 Ø2 — 10 15 — XTAL 1 Ø1 — 11                                 | The XTAL 1 and 2 inputs allow for an external crystal connection which produces a Ø1 and Ø2 master clock for the 8800b. The SYNC input from the 8080 (CPU) and internal timing generate a LOW status strobe (STSTB) signal. The reset in (RESIN) input generates a RESET output to condition the 8080 (CPU). A HIGH ready in (RDYIN) input generates a READY output to enable the CPU.                               |

Table 3-1. Symbol Definitions - Continued

| NAME       | LOGIC<br>SYMBOL                                                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

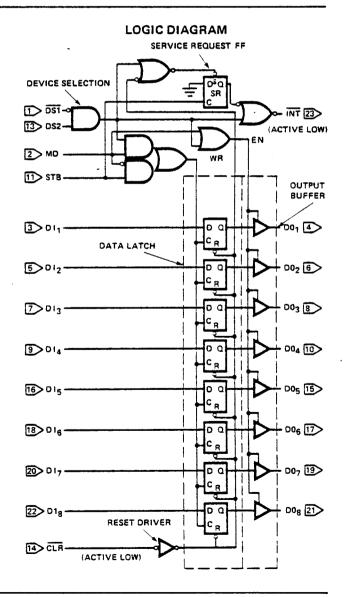

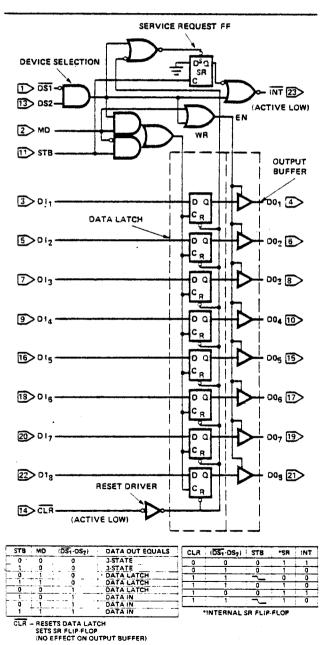

| Data Latch | 3 5 7 9 22 20 18 16  DS1  DS2  MD  STB  DO0  DO7  4 8 8 10 21 19 17 15 | The data latch is used to store or transfer data on the $\mathrm{D0}_0$ - $\mathrm{D0}_7$ outputs by affecting the data latch control inputs. There are several different ways used to store data or transfer it to the data latch.  When data is presented to the $\mathrm{DI}_0$ - $\mathrm{DI}_7$ inputs and the device selection 2 (DS2), mode MD, and strobe (STB) are HIGH, a LOW device selection 1 ( $\overline{\mathrm{DS1}}$ ) allows the input data to be present on the $\mathrm{D0}_0$ - $\mathrm{D0}_7$ outputs.  When data is presented to the $\mathrm{DI}_0$ - $\mathrm{DI}_7$ inputs and MD and STB are HIGH, a HIGH DS2 and LOW $\overline{\mathrm{DS1}}$ allow the input data to be present on the $\mathrm{D0}_0$ - $\mathrm{D0}_7$ outputs.  When data is presented to the $\mathrm{DI}_0$ - $\mathrm{DI}_7$ inputs and $\overline{\mathrm{DS1}}$ and MD are LOW, a HIGH DS2 and STB allow the input data to be present on the $\mathrm{D0}_0$ - $\mathrm{D0}_7$ outputs.  When data is presented to the $\mathrm{DI}_0$ - $\mathrm{DI}_7$ inputs, and MD and DS2 are HIGH with $\overline{\mathrm{DS1}}$ LOW, the input data is directly transferred to the $\mathrm{D0}_0$ - $\mathrm{D0}_7$ outputs as long as these states are present. |

Table 3-1. Symbol Definitions - Continued

| NAME                                    | LOGIC<br>Symbol        | DESCRIPTION                                                                                                                                                                                                                              |

|-----------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROM (programmable read only memory)  2 | 03 D04 D05 D06 D07 D08 | When the chip select input (CS) is LOW, the binary address at input A <sub>O</sub> through A <sub>T</sub> is decoded to select one of 256 address locations. The data is present on the DO <sub>I</sub> through DO <sub>8</sub> outputs. |

## 3-3. INTEL 8080 MICROCOMPUTER SYSTEMS USER'S INFORMATION

Pages 3-9 through 3-38 are excerpts from the Intel 8080 Micro-computer Systems User's Manual, reprinted by permission of Intel Corporation, Copyright, 1975. Included is information on the 8080A Microprocessor, the 8212 Input/Output Port, the 8216 Bi-Directional Bus Driver, and the 8224 Clock Generator and Driver. It is recommended that a good understanding of these integrated circuit operations be developed before continuing this section.

# Silicon Gate MOS 8080 A

## SINGLE CHIP 8-BIT N-CHANNEL MICROPROCESSOR

The 8080A is functionally and electrically compatible with the Intel® 8080.

- TTL Drive Capability

- 2 μs Instruction Cycle

- Powerful Problem Solving Instruction Set

- Six General Purpose Registers and an Accumulator

- Sixteen Bit Program Counter for Directly Addressing up to 64K Bytes of Memory

- Sixteen Bit Stack Pointer and Stack Manipulation Instructions for Rapid Switching of the Program Environment

- Decimal, Binary and Double Precision Arithmetic

- Ability to Provide Priority Vectored Interrupts

- 512 Directly Addressed I/O Ports

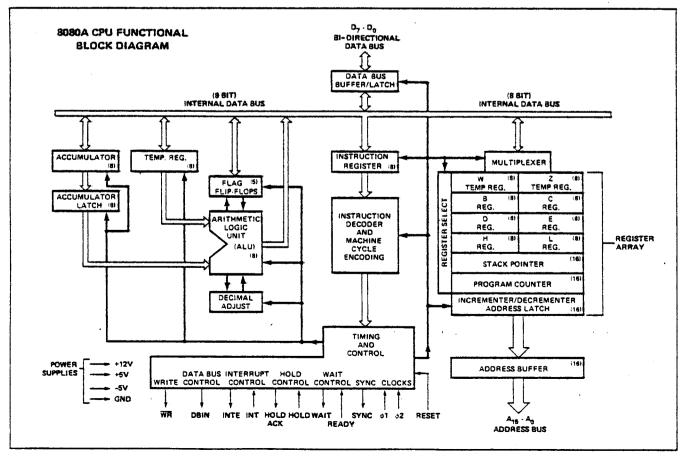

The Intel® 8080A is a complete 8-bit parallel central processing unit (CPU). It is fabricated on a single LSI chip using Intel's n-channel silicon gate MOS process. This offers the user a high performance solution to control and processing applications. The 8080A contains six 8-bit general purpose working registers and an accumulator. The six general purpose registers may be addressed individually or in pairs providing both single and double precision operators. Arithmetic and logical instructions set or reset four testable flags. A fifth flag provides decimal arithmetic operation.

The 8080A has an external stack feature wherein any portion of memory may be used as a last in/first out stack to store/ retrieve the contents of the accumulator, flags, program counter and all of the six general purpose registers. The sixteen bit stack pointer controls the addressing of this external stack. This stack gives the 8080A the ability to easily handle multiple level priority interrupts by rapidly storing and restoring processor status. It also provides almost unlimited subroutine nesting. This microprocessor has been designed to simplify systems design. Separate 16-line address and 8-line bi-directional data

This microprocessor has been designed to simplify systems design. Separate 16-line address and 8-line bi-directional data busses are used to facilitate easy interface to memory and I/O. Signals to control the interface to memory and I/O are provided directly by the 8080A. Ultimate control of the address and data busses resides with the HOLD signal. It provides the ability to suspend processor operation and force the address and data busses into a high impedance state. This permits ORtying these busses with other controlling devices for (DMA) direct memory access or multi-processor operation.

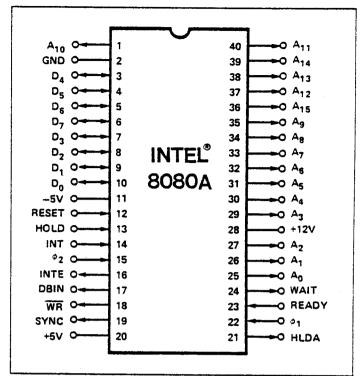

#### 8080A FUNCTIONAL PIN DEFINITION

The following describes the function of all of the 8080A I/O pins. Several of the descriptions refer to internal timing periods.

#### A<sub>15</sub>.A<sub>0</sub> (output three-state)

ADDRESS BUS; the address bus provides the address to memory (up to 64K 8-bit words) or denotes the I/O device number for up to 256 input and 256 output devices.  $A_0$  is the least significant address bit.

#### D<sub>7</sub>-D<sub>0</sub> (input/output three-state)

DATA BUS; the data bus provides bi-directional communication between the CPU, memory, and I/O devices for instructions and data transfers. Also, during the first clock cycle of each machine cycle, the 8080A outputs a status word on the data bus that describes the current machine cycle. Do is the least significant bit.

#### SYNC (output)

SYNCHRONIZING SIGNAL; the SYNC pin provides a signal to indicate the beginning of each machine cycle.

#### **DBIN** (output)

DATA BUS IN; the DBIN signal indicates to external circuits that the data bus is in the input mode. This signal should be used to enable the gating of data onto the 8080A data bus from memory or I/O.

#### **READY** (input)

READY; the READY signal indicates to the 8080A that valid memory or input data is available on the 8080A data bus. This signal is used to synchronize the CPU with slower memory or I/O devices. If after sending an address out the 8080A does not receive a READY input, the 8080A will enter a WAIT state for as long as the READY line is low. READY can also be used to single step the CPU.

#### WAIT (output)

WAIT; the WAIT signal acknowledges that the CPU is in a WAIT state.

#### WR (output)

WRITE; the  $\overline{WR}$  signal is used for memory WRITE or I/O output control. The data on the data bus is stable while the  $\overline{WR}$  signal is active low ( $\overline{WR}$  = 0).

#### **HOLD** (input)

HOLD; the HOLD signal requests the CPU to enter the HOLD state. The HOLD state allows an external device to gain control of the 8080A address and data bus as soon as the 8080A has completed its use of these buses for the current machine cycle. It is recognized under the following conditions:

- the CPU is in the HALT state.

- the CPU is in the T2 or TW state and the READY signal is active. As a result of entering the HOLD state the CPU ADDRESS BUS  $(A_{15}-A_0)$  and DATA BUS  $(D_7-D_0)$  will be in their high impedance state. The CPU acknowledges its state with the HOLD ACKNOWLEDGE (HLDA) pin.

#### **HLDA** (output)

HOLD ACKNOWLEDGE; the HLDA signal appears in response to the HOLD signal and indicates that the data and address bus

Pin Configuration

will go to the high impedance state. The HLDA signal begins at:

- T3 for READ memory or input.

- The Clock Period following T3 for WRITE memory or OUT-PUT operation.

In either case, the HLDA signal appears after the rising edge of  $\phi_1$  and high impedance occurs after the rising edge of  $\phi_2$ .

#### INTE (output)

INTERRUPT ENABLE; indicates the content of the internal interrupt enable flip/flop. This flip/flop may be set or reset by the Enable and Disable Interrupt instructions and inhibits interrupts from being accepted by the CPU when it is reset. It is automatically reset (disabling further interrupts) at time T1 of the instruction fetch cycle (M1) when an interrupt is accepted and is also reset by the RESET signal.

#### INT (input)

INTERRUPT REQUEST; the CPU recognizes an interrupt request on this line at the end of the current instruction or while halted. If the CPU is in the HOLD state or if the Interrupt Enable flip/flop is reset it will not honor the request.

#### RESET (input)[1]

RESET; while the RESET signal is activated, the content of the program counter is cleared. After RESET, the program will start at location 0 in memory. The INTE and HLDA flip/flops are also reset. Note that the flags, accumulator, stack pointer, and registers are not cleared.

Vss Ground Reference.

VDD +12 ± 5% Volts.

Vcc +5 ± 5% Volts.

VBB -5 ±5% Volts (substrate bias).

$\phi_1$ ,  $\phi_2$  2 externally supplied clock phases. (non TTL compatible)

#### **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias                                                                |                 |

|---------------------------------------------------------------------------------------|-----------------|

| Storage Temperature                                                                   | -65°C to +150°C |

| All Input or Output Voltages                                                          |                 |

| With Respect to VBB                                                                   | 0.3V to +20V    |

| V <sub>CC</sub> , V <sub>DD</sub> and V <sub>SS</sub> With Respect to V <sub>BB</sub> | -0.3V to +20V   |

| Power Dissipation                                                                     | 1.5W            |

\*COMMENT: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### D.C. CHARACTERISTICS

$T_A = 0^{\circ}$ C to  $70^{\circ}$ C,  $V_{DD} = +12$ V ± 5%,  $V_{CC} = +5$ V ± 5%,  $V_{BB} = -5$ V ± 5%,  $V_{SS} = 0$ V, Unless Otherwise Noted.

| Symbol              | Parameter                                    | Min.               | Тур.                                | Max.                 | Unit                                                                           | Test Condition                                      |  |  |  |  |

|---------------------|----------------------------------------------|--------------------|-------------------------------------|----------------------|--------------------------------------------------------------------------------|-----------------------------------------------------|--|--|--|--|

| VILC                | Clock Input Low Voltage                      | V <sub>SS</sub> -1 |                                     | V <sub>SS</sub> +0.8 | ٧                                                                              |                                                     |  |  |  |  |

| V <sub>IHC</sub>    | Clock Input High Voltage                     | 9.0                |                                     | V <sub>DD</sub> +1   | ٧                                                                              |                                                     |  |  |  |  |

| VIL                 | Input Low Voltage                            | V <sub>SS</sub> -1 |                                     | V <sub>SS</sub> +0.8 | ٧                                                                              |                                                     |  |  |  |  |

| V <sub>IH</sub>     | Input High Voltage                           | 3.3                |                                     | V <sub>CC</sub> +1   | ٧                                                                              |                                                     |  |  |  |  |

| Vol                 | Output Low Voltage                           |                    | Annual representation of the second | 0.45                 | ٧                                                                              | $\int_{OL} = 1.9 \text{mA on all outputs,}$         |  |  |  |  |

| V <sub>СН</sub>     | Output High Voltage 3.7                      |                    |                                     |                      | ٧                                                                              | lo <sub>H</sub> = −150μA.                           |  |  |  |  |

| IDD (AV)            | Avg. Power Supply Current (V <sub>DD</sub> ) |                    | 40                                  | 70                   | mΑ                                                                             |                                                     |  |  |  |  |

| ICC (AV)            | Avg. Power Supply Current (V <sub>CC</sub> ) |                    | 60                                  | 80                   | mA                                                                             | Operation<br>T <sub>CY</sub> = .48 μsec             |  |  |  |  |

| IBB (AV)            | Avg. Power Supply Current (V <sub>BB</sub> ) |                    | .01                                 | 1                    | mA                                                                             |                                                     |  |  |  |  |

| I <sub>IL</sub>     | Input Leakage                                |                    |                                     | ±10                  | μΑ                                                                             | V <sub>SS</sub> ≤ V <sub>IN</sub> ≤ V <sub>CC</sub> |  |  |  |  |

| <sup>I</sup> CL     | Clock Leakage                                |                    |                                     | ±10                  | μΑ                                                                             | V <sub>SS</sub> € VCLOCK € VDD                      |  |  |  |  |

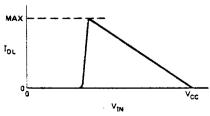

| I <sub>DL</sub> [2] | Data Bus Leakage in Input Mode               |                    | -100<br>-2.0                        | μA<br>mA             | $V_{SS} \le V_{IN} \le V_{SS} + 0.8V$<br>$V_{SS} + 0.8V \le V_{IN} \le V_{CC}$ |                                                     |  |  |  |  |

| l <sub>F</sub> L    | Address and Data Bus Leakage<br>During HOLD  |                    |                                     | +10                  | μΑ                                                                             | VADDR/DATA = VCC<br>VADDR/DATA = VSS + 0.45V        |  |  |  |  |

#### CAPACITANCE

$T_A = 25^{\circ}C$   $V_{CC} = V_{DD} = V_{SS} = 0V$ ,  $V_{BB} = -5V$

| Symbol         | Parameter          | Тур. | Max. | Unit | Test Condition              |  |  |  |  |

|----------------|--------------------|------|------|------|-----------------------------|--|--|--|--|

| С <sub>ф</sub> | Clock Capacitance  | 17   | 25   | pf   | f <sub>c</sub> = 1 MHz      |  |  |  |  |

| CIN            | Input Capacitance  | 6    | 10   | pf   | Unmeasured Pins             |  |  |  |  |

| Cout           | Output Capacitance | 10   | 20   | ρf   | Returned to V <sub>SS</sub> |  |  |  |  |

#### NOTES

- 1. The RESET signal must be active for a minimum of 3 clock cycles.

- 2. When DBIN is high and  $\rm V_{IN}>V_{IH}$  an internal active pull up will be switched onto the Data Bus.

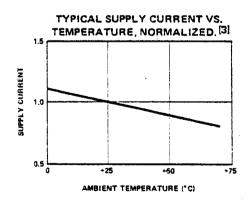

- 3.  $\Delta I$  supply /  $\Delta T_A = -0.45\%$ /° C.

#### A.C. CHARACTERISTICS

$T_A = 0^{\circ}$ C to  $70^{\circ}$ C,  $V_{DD} = +12$ V  $\pm$  5%,  $V_{CC} = +5$ V  $\pm$  5%,  $V_{BB} = -5$ V  $\pm$  5%,  $V_{SS} = 0$ V, Unless Otherwise Noted

| Symbol                          | Parameter                                                                            | Min. | Max. | Unit  | Test Condition           |

|---------------------------------|--------------------------------------------------------------------------------------|------|------|-------|--------------------------|

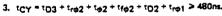

| t <sub>CY</sub> [3]             | Clock Period                                                                         | 0.48 | 2.0  | μsec  | - See Gondicion          |

| t <sub>r</sub> , t <sub>f</sub> | Clock Rise and Fall Time                                                             | 0    | 50   | nsec  |                          |

| <b>t</b> ø1                     | φ <sub>1</sub> Pulse Width                                                           | 60   |      | nsec  |                          |

| t <sub>ø2</sub>                 | $\phi_2$ Pulse Width                                                                 | 220  |      | nsec  |                          |

| t <sub>D1</sub>                 | Delay $\phi_1$ to $\phi_2$                                                           | 0    |      | n sec |                          |

| D2                              | Delay $\phi_2$ to $\phi_1$                                                           | 70   |      | nsec  |                          |

| t <sub>D3</sub>                 | Delay $\phi_1$ to $\phi_2$ Leading Edges                                             | 80   |      | n sec |                          |

| t <sub>DA</sub> [2]             | Address Output Delay From $\phi_2$                                                   |      | 200  | nsec  |                          |

| <sup>[2]</sup>                  | Data Output Delay From $\phi_2$                                                      |      | 220  | n sec | - C <sub>L</sub> = 100pf |

| toc <sup>[2]</sup>              | Signal Output Delay From $\phi_1$ , or $\phi_2$ (SYNC, $\overline{WR}$ , WAIT, HLDA) |      | 120  | nsec  | =                        |

| t <sub>DF</sub> [2]             | DBIN Delay From $\phi_2$                                                             | 25   | 140  | n sec | - C <sub>L</sub> = 50pf  |

| t <sub>D1</sub> [1]             | Delay for Input Bus to Enter Input Mode                                              |      | tDF  | nsec  |                          |

| t <sub>DS1</sub>                | Data Setup Time During $\phi_1$ and DBIN                                             | 30   |      | n sec |                          |

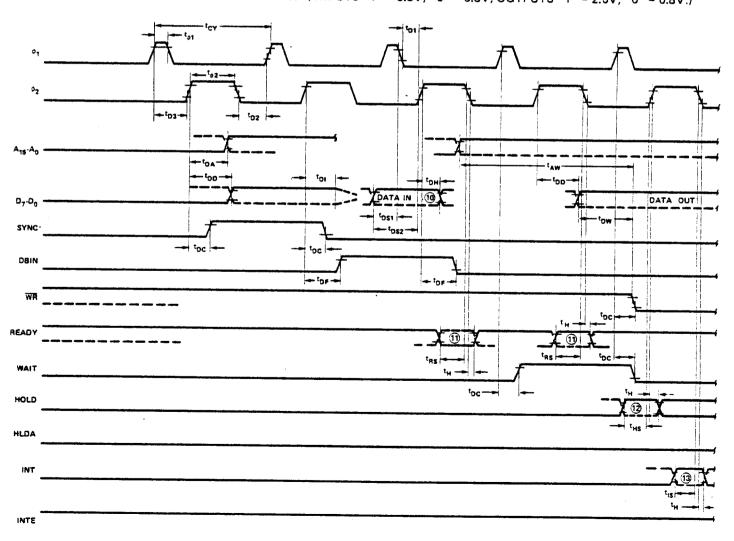

## TIMING WAVEFORMS [14]

(Note: Timing measurements are made at the following reference voltages: CLOCK "1" = 8.0V "0" = 1.0V; INPUTS "1" = 3.3V, "0" = 0.8V; OUTPUTS "1" = 2.0V, "0" = 0.8V.)

#### A.C. CHARACTERISTICS (Continued)

$T_A = 0^{\circ}C$  to  $70^{\circ}C$ ,  $V_{DD} = +12V \pm 5\%$ ,  $V_{CC} = +5V \pm 5\%$ ,  $V_{BB} = -5V \pm 5\%$ ,  $V_{SS} = 0V$ , Unless Otherwise Noted

| Symbol              | Parameter ·                                                   | Min. | Max. | Unit  | Test Condition                                                               |

|---------------------|---------------------------------------------------------------|------|------|-------|------------------------------------------------------------------------------|

| <sup>t</sup> DS2    | Data Setup Time to $\phi_2$ During DBIN                       | 150  |      | n sec |                                                                              |

| t <sub>OH</sub> [1] | Data Hold Time From $\phi_2$ During DBIN                      | [1]  | -    | n sec |                                                                              |

| t <sub>IE</sub> [2] | INTE Output Delay From $\phi_2$                               |      | 200  | nsec  | C <sub>L</sub> = 50pf                                                        |

| tRS                 | READY Setup Time During $\phi_2$                              | 120  |      | nsec  |                                                                              |

| <sup>t</sup> HS     | HOLD Setup Time to $\phi_2$                                   | 140  |      | nsec  |                                                                              |

| tis                 | INT Setup Time During $\phi_2$ (During $\phi_1$ in Halt Mode) | 120  |      | n sec |                                                                              |

| tн                  | Hold Time From $\phi_2$ (READY, INT, HOLD)                    | 0    |      | n sec |                                                                              |

| <sup>t</sup> FD     | Delay to Float During Hold (Address and Data Bus)             |      | 120  | nsec  |                                                                              |

| t <sub>AW</sub> [2] | Address Stable Prior to WR                                    | [5]  |      | n sec | ] ]                                                                          |

| t <sub>DW</sub> [2] | Output Data Stable Prior to WR                                | [6]  |      | n sec |                                                                              |

| two <sup>[2]</sup>  | Output Data Stable From WR                                    | [7]  |      | n sec |                                                                              |

| twA <sup>[2]</sup>  | Address Stable From WR                                        | [7]  |      | n sec | C <sub>L</sub> =100pf: Address, Data<br>C <sub>L</sub> =50pf: WR, HLDA, DBIN |

| t <sub>HF</sub> [2] | HLDA to Float Delay                                           | [8]  |      | nsec  |                                                                              |

| twF [2]             | WR to Float Delay                                             | [9]  |      | nsec  |                                                                              |

| t <sub>AH</sub> [2] | Address Hold Time After DBIN During HLDA                      | -20  |      | n sec |                                                                              |

- 1. Data input should be enabled with OBIN status. No bus conflict can then occur and data hold time is assured. tDH = 50 ns or tDF, whichever is less.

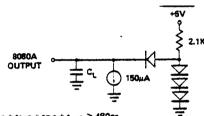

- 2. Load Circuit.

## TYPICAL A OUTPUT DELAY VS. A CAPACITANCE OUTPUT DELAY (ns) +10 -10 -50 +100 2 CAPACITANCE (pf) (CACTUAL - CSPEC)

- 4. The following are relevant when interfacing the 8080A to devices having  $V_{1H}$  = 3.3V:

- a) Maximum output rise time from .8V to 3.3V = 100ns @ Ci\_ = SPEC.

- b) Output delay when measured to 3.0V = SPEC +60ns @ CL = SPEC.

- c) If C<sub>L</sub> ≠ SPEC, add .6ns/pF if C<sub>L</sub>> C<sub>SPEC</sub>, subtract .3ns/pF (from modified delay) if C<sub>L</sub> < C<sub>SPEC</sub>.

- 5. tAW = 2 tCY -tD3 -tro2 -140nsec.

- 5. tpw = tcy -tp3 -tro2 = 170nsec.

7. If not HLDA, twD = twA = tp3 + tro2 +10ns. If HLDA, twD = twA = twF.

- 8.  $tHF = tD3 + t_{r\phi2} 50ns$ .

- tWF = t03 + tro2 -10ns

- 10. Data in must be stable for this period during DBIN 'T3. Both tDS1 and tDS2 must be satisfied.

- 11. Ready signal must be stable for this period during  $T_2$  or  $T_W$ . (Must be externally synchronized.)

- 12. Hold signal must be stable for this period during  $T_2$  or  $T_W$  when entering hold mode, and during  $T_3$ ,  $T_4$ ,  $T_5$ and TWH when in hold mode. (External synchronization is not required.)

- 13. Interrupt signal must be stable during this period of the last clock cycle of any instruction in order to be recognized on the following instruction. (External synchronization is not required.)

- 14. This timing diagram shows timing relationships only; it does not represent any specific machine cycle.

#### INSTRUCTION SET

The accumulator group instructions include arithmetic and logical operators with direct, indirect, and immediate addressing modes.

Move, load, and store instruction groups provide the ability to move either 8 or 16 bits of data between memory, the six working registers and the accumulator using direct, indirect, and immediate addressing modes.

The ability to branch to different portions of the program is provided with jump, jump conditional, and computed jumps. Also the ability to call to and return from subroutines is provided both conditionally and unconditionally. The RESTART (or single byte call instruction) is useful for interrupt vector operation.

Double precision operators such as stack manipulation and double add instructions extend both the arithmetic and interrupt handling capability of the 8080A. The ability to

increment and decrement memory, the six general registers and the accumulator is provided as well as extended increment and decrement instructions to operate on the register pairs and stack pointer. Further capability is provided by the ability to rotate the accumulator left or right through or around the carry bit.

Input and output may be accomplished using memory addresses as I/O ports or the directly addressed I/O provided for in the 8080A instruction set.

The following special instruction group completes the 8080A instruction set: the NOP instruction, HALT to stop processor execution and the DAA instructions provide decimal arithmetic capability. STC allows the carry flag to be directly set, and the CMC instruction allows it to be complemented. CMA complements the contents of the accumulator and XCHG exchanges the contents of two 16-bit register pairs directly.

#### Data and Instruction Formats

Data in the 8080A is stored in the form of 8-bit binary integers. All data transfers to the system data bus will be in the same format.

The program instructions may be one, two, or three bytes in length. Multiple byte instructions must be stored in successive words in program memory. The instruction formats then depend on the particular operation executed.

One Byte Instructions

D7 D6 D5 D4 D3 D2 D1 D0 OP CODE

TYPICAL INSTRUCTIONS

Register to register, memory reference, arithmetic or logical, rotate, return, push, pop, enable or disable Interrupt instructions

Two Byte Instructions

D<sub>7</sub> D<sub>6</sub> D<sub>5</sub> D<sub>4</sub> D<sub>3</sub> D<sub>2</sub> D<sub>1</sub> D<sub>0</sub> OP CODE

D<sub>7</sub> D<sub>6</sub> D<sub>5</sub> D<sub>4</sub> D<sub>3</sub> D<sub>2</sub> D<sub>1</sub> D<sub>0</sub> OPERAND

Immediate mode or I/O instructions

Three Byte Instructions

D<sub>7</sub> D<sub>6</sub> D<sub>5</sub> D<sub>4</sub> D<sub>3</sub> D<sub>2</sub> D<sub>1</sub> D<sub>0</sub> OP CODE

D<sub>7</sub> D<sub>6</sub> D<sub>5</sub> D<sub>4</sub> D<sub>3</sub> D<sub>2</sub> D<sub>1</sub> D<sub>0</sub> LOW ADD

LOW ADDRESS OR OPERAND 1

Jump, call or direct load and store instructions

D<sub>7</sub> D<sub>6</sub> D<sub>5</sub> D<sub>4</sub> D<sub>3</sub> D<sub>2</sub> D<sub>1</sub> D<sub>0</sub> HIGH ADDRESS OR OPERAND 2

For the 8080A a logic "1" is defined as a high level and a logic "0" is defined as a low level.

#### **INSTRUCTION SET**

#### **Summary of Processor Instructions**

| Mnemonic             | Oescription                                     | 07   | De | _ |   |   | odel<br>3 Dz |   | 1 00   | Clock [2]<br>Cycles | Mnemonic     | Description                                 | D <sub>7</sub> | D <sub>6</sub> | _ | tructi<br>0 <sub>4</sub> |   |    |   | D <sub>O</sub> | Clock <sup>[2]</sup><br>Cycles |

|----------------------|-------------------------------------------------|------|----|---|---|---|--------------|---|--------|---------------------|--------------|---------------------------------------------|----------------|----------------|---|--------------------------|---|----|---|----------------|--------------------------------|

| MOV <sub>r1-r2</sub> | Move register to register                       | 0    | 1  | D | 0 | Ð | s            | s | s      | 5                   | RZ           | Return on zero                              | 1              | 1              | 0 | 0                        | 1 | 0  | 0 | 0              | 5/11                           |

| MOV M, r             | Move register to memory                         | 0    | 1  | 1 | 1 | 0 | S            | S | \$     | 7                   | RNZ          | Return on no zero                           | 1              | 1              | 0 | 0                        | 0 | 0  | C | 0              | 5/11                           |

| MQV r, M             | Move memory to register                         | 8    | 1  | 0 | 0 | 0 | 1            | 1 | 0      | 7                   | RP           | Return on positive                          | 1              | 1              | 1 | i                        | 0 | 0  | 0 | 0              | 5/11                           |

| HLT                  | Helt .                                          | 0    | 1  | 1 | 1 | 0 | 1            | 1 | 0      | 7                   | RM           | Return on minus                             | 1              | 1              | 1 | 1                        | 1 | 0  | 0 | 0              | 5/11                           |

| MVIr                 | Move immediate register                         | Q    | 0  | 0 | D | 0 | 1            | 1 | 0      | 7                   | RPE          | Return on parity even                       | 1              | 1              | 1 | G                        | 1 | ũ  | 0 | 9              | 5/11                           |

| MVIM                 | Move immediate memory                           | 0    | 0  | 1 | 1 | 0 | 1            | 1 | 0      | 10                  | RPO          | Return on parity odd                        | 1              | 1              | 1 | 0                        | 0 | 0  | ũ | 0              | 5/11                           |

| INR r                | Increment register                              | 0    | 0  | 0 | 0 | 0 | 1            | 0 | 0      | 5                   | RST          | Restart                                     | 1              | 1              | Α | Α                        | Α | 1  | 1 | 1              | 11                             |

| OCR r                | Decrement register                              | 0    | 0  | 0 | 0 | 0 | 1            | 0 | 1      | 5                   | IN           | Input                                       | 1              | 1              | 0 | 1                        | 1 | 0  | 1 | 1              | 10                             |

| INR M                | Increment memory                                | 0    | 0  | 1 | 1 | 0 | 1            | 0 | 9      | 10                  | OUT          | Output                                      | 1              | 1              | 0 | 1                        | 0 | 0  | 1 | 1              | 10                             |

| OCR M                | Decrement memory                                | 0    | 0  | 1 | 1 | 0 | 1            | 0 | 1      | 10                  | LXI B        | Load immediate register                     | 0              | Q              | Q | 0                        | 0 | 0  | 0 | 1              | 10                             |

| 1 00A                | Add register to A                               | 1    | 0  | 0 | 0 | 1 | S            | Ş | S      | 4                   |              | Pair B & C                                  | _              | _              | _ | _                        | _ | _  | _ |                |                                |

| 1 30A                | Add register to A with carry                    | 1    | 0  | 0 | 0 | • | S            | S | S      | 4                   | LXI 0        | Load immediate register                     | 0              | 0              | 0 | 1                        | 0 | 0  | 0 | 1              | 10                             |

| 1 8UZ                | Subtract register from A                        | 1    | 0  | 0 | 1 | 0 | S            | S | S<br>S | 4                   |              | Pair D & E                                  | _              | _              |   | _                        | _ | _  | _ |                |                                |

| S88 r                | Subtract register from A                        | '    | U  | U | , | 1 | 3            | 3 | 3      | •                   | LXIH         | Load immediate register                     | 0              | 0              | 1 | 0                        | 0 | 0  | G | 1              | 10                             |

| ANA r                | with borrow And register with A                 | 1    | 0  | , | a | 0 | s            | s | s      | 4                   |              | Pair H & L                                  | _              | _              |   |                          | _ |    | _ |                |                                |

| XRA r                | •                                               | i    | 0  | ; | 0 | 1 | S            | S | S      | 4                   | LXI SP       | Load immediate stack pointer                | 0              | 0              | 1 | 1                        | 0 | 0  | 0 | 1              | 10                             |

| ORA r                | Exclusive Or register with A Or register with A | 'n   | 0  | , | 1 | å | S            | S | S      | 4                   | PUSH 8       | Push register Pair 8 & C on                 | 1              | 1              | 0 | 0                        | 0 | 1  | 0 | 1              | 11                             |

| CMPr                 | Compare register with A                         | i    | ā  | 1 | í | ĭ | Š            | Š | Š      | 4                   | aucu n       | Stack                                       |                |                | • |                          |   |    |   |                | ••                             |

| ADD M                | Add memory to A                                 | i    | ō  | à | à | ò | 1            | 1 | a      | 7                   | PUSH D       | Push register Pair O & E on                 | 1              | 1              | 0 | 1                        | G | 1  | 0 | 1              | 11                             |

| ADC M                | Add memory to A with carry                      | i    | ā  | Ď | ō | 1 | i            | i | ñ      | 7                   | PUSH H       | Stack                                       |                |                |   |                          | • |    | • |                | 11                             |

| SUB M                | Subtract memory from A                          | i    | 8  | 0 | i | ò | 1            | i | o      | 7                   | FUSHIN       | Push register Pair H & L on stack           | 1              | 1              | 1 | 8                        | 0 | 1  | 0 | 1              | 13                             |

| 588 M                | Subtract memory from A with borrow              | i    | 0  | ō | i | ī | 1            | 1 | å      | 7                   | Push PSW     | Push A and Flags<br>on stack                | 1              | 1              | 1 | 1                        | G | 1  | 0 | 1              | 11                             |

| ANA M                | And memory with A                               | 1    | 0  | 1 | 0 | 0 | 1            | 1 | 0      | 7<br>7              | POP 8        | Pop register pair B & C off                 | 1              | 1              | 0 | 0                        | 0 | 0  | 0 | 1              | 10                             |

| M ARX                | Exclusive Or memory with A                      | 1    | 0  | ! | 0 |   | !            | 1 | 0      | 7                   |              | stack                                       | _              |                | _ |                          | _ | _  | _ | _              |                                |

| ORA M                | Or memory with A                                | 1    | 0  | 1 | 1 | 0 | 1            | i | 0      | 7                   | POP O        | Pop register pair 0 & E off                 | 1              | 1              | 0 | 1                        | 0 | 0  | 0 | 1              | 10                             |

| CMP M                | Compare memory with A                           | 1    | •  | 0 | Ó | Ó | 'i           | 1 | 0      | 7                   | 2004         | stack                                       |                |                |   | •                        |   |    |   |                | 10                             |

| ADI<br>ACI           | Add immediate to A Add immediate to A with      | ,    | 1  | G | 0 | · | 1            | 1 | 0      | 7                   | POP H        | Pop register pair H & L off                 | 1              | 1              | 1 | 0                        | 0 | 0  | 0 | 1              | 10                             |

|                      | carry                                           |      |    |   |   | ď | 1            | , | 0      | .7                  | POP PSW      | stack 6 Pop A and Flags                     | 1              | 1              | 1 | 1                        | 0 | 0  | 0 | 1              | 10                             |

| SUI                  | Subtract immediate from A                       | 1    | 1  | 0 | 1 | ' | 1            | 1 | G      | 7                   |              | off stack                                   |                |                |   |                          | _ |    |   |                | 40                             |

| S81                  | Subtract immediate from A                       | ,    | 1  | U | 1 | , | '            | • | U      | ,                   | STA          | Store A direct                              | 0              | 0              | 1 | 1                        | 0 | 0  | 1 | 0              | 13                             |

| ANI                  | with borrow And immediate with A                | 1    | 1  | 1 | a |   |              |   | O      | 7                   | LDA          | Load A direct                               | 0              | 0              | 1 | 1                        | 1 | 0  | 1 | 0<br>1         | 13<br>4                        |

| XRI                  | Exclusive Or immediate with                     | i    | 1  | 1 | Ö | 1 | i            | i | Ō      | 7                   | XCHG<br>XTHL | Exchange D & E, H & L<br>Registers          | 1              | •              | • |                          | , | _  | 1 |                | 18                             |

| CRI                  | Or immediate with A                             | 1    | 1  | 1 | 1 | n | 1            | 1 | a      | 7                   | SPHL         | Exchange top of stack, H & L                | 1              | 1              | ! | 0                        | 0 | 0  | 1 | 1              | 5                              |

| CPI                  | Compare immediate with A                        | i    | 1  | , | i | 1 | í            | i | ū      | ;                   | PCHL         | H & L to stack pointer                      | •              | i              | 1 | Ġ                        | 1 | ß  | 0 | i              | 5                              |

| RLC                  | Rotate A left                                   | ò    | á  | à | à | à | i            | i | 1      | 4                   | DAD B        | H & L to program counter Add B & C to H & L | Ġ              | á              | ò | 0                        | 1 | ů  | G | i              | 10                             |

| RRC                  | Rotate A right                                  | ā    | G  | ō | ā | 1 | i            | 1 | i      | 4                   | DAOD         | Add D & E to H & L                          | 0              | n              | a | 1                        | ; | ū  | a | ì              | 10                             |

| RAL                  | Rotate A left through carry                     | ō    | ō  | ō | ī | Ó | i            | 1 | 1      | 4                   | DADH         | Add H & L to H & L                          | Ö              | a              | 1 | ò                        | 1 | ă  | a | i              | 10                             |

| RAR                  | Rotate A right through                          | Ŏ    | Õ  | ō | 1 | 1 | 1            | 1 | 1      | 4                   | DAD SP       | Add stack pointer to H & L                  | ō              | o              | 1 | 1                        | 1 | õ  | 0 | i              | 10                             |

|                      | Carry                                           | •    | •  | - | - |   | -            |   |        |                     | STAX 8       | Store A indirect                            | Ö              | ŏ              | Ó | à                        | ò | ā  | 1 | ò              | 7                              |

| JMP                  | Jump unconditional                              | 1    | 1  | Q | 0 | 0 | 0            | 1 | 1      | 10                  | STAX D       | Store A indirect                            | õ              | ñ              | ō | ī                        | ā | ā  | i | ă              | 7                              |

| JC                   | Jump on carry                                   | 1    | 1  | 0 | 1 | 1 | 0            | 1 | 0      | 10                  | LDAX B       | Load A indirect                             | ō              | ō              | ō | o                        | 1 | õ  | 1 | ā              | 7                              |

| JNC                  | Jump on no carry                                | 1    | 1  | 0 | 1 | 0 | 0            | 1 | 0      | 10                  | LDAX D       | Load A indirect                             | ā              | ō              | ō | ĭ                        | i | ŏ  | i | Ğ              | 7                              |

| JZ                   | Jump on zero                                    | 1    | 1  | 0 | 0 | 1 | 0            | 1 | 0      | 10                  | INX B        | Increment B & C registers                   | ō              | ū              | ō | Ö                        | ò | ō  | i | ī              | 5                              |

| JNZ                  | Jump an no zera                                 | 1    | 1  | 0 | 0 | 0 | 0            | 1 | 0      | 10                  | INX O        | Increment 0 & E registers                   | Ö              | ō              | ā | 1                        | 0 | ā  | 1 | 1              | 5                              |

| JP                   | Jump on positive                                | 1    | 1  | 1 | 1 | 0 | 0            | 1 | 0      | 10                  | INX H        | Increment H & L registers                   | Ŏ              | ā              | 1 | Ġ                        | ō | ġ. | 1 | t              | 5                              |

| JM                   | Jump on minus                                   | 1    | 1  | 1 | 1 | 1 | 0            | 1 | 0      | 10                  | INX SP       | increment stack pointer                     | ō              | 0              | 1 | 1                        | 0 | ā  | 1 | 1              | 5                              |

| JPE                  | Jump on parity even                             | - 1  | 1  | 1 | 0 | 1 | 0            | 1 | 0      | 10                  | DCX 8        | Decrement B & C                             | 0              | 0              | 0 | 0                        | 1 | 0  | 1 | 1              | 5                              |

| 160                  | Jump on parity odd                              | 1    | 1  | 1 | 0 | 0 | 0            | 1 | 0      | 10                  | DCX D        | Decrement D & E                             | 0              | 0              | G | 1                        | 1 | 0  | 1 | 1              | 5                              |

| CALL                 | Call unconditional                              | - 1, | 1  | 0 | 0 | 1 | 1            | 0 | 1      | 17                  | DCX H        | Decrement H & L                             | Ō              | ā              | 1 | 0                        | 1 | 0  | 1 | 1              | 5                              |

| CC                   | Call on carry                                   | 1    | 1  | 0 | 1 | 1 | 1            | 0 | 0      | 11/17               | OCX SP       | Decrement stack pointer                     | Ò              | 0.             | 1 | 1                        | 1 | 0  | 1 | 1              | 5                              |

| CNC                  | Call on no carry                                | 1    | 1  | 0 | 1 | 0 | 1            | 0 | 0      | 11/17               | CMA          | Complement A                                | 0              | 0              | 1 | 0                        | 1 | 1  | 1 | 1              | 4                              |

| CZ                   | Call on zero                                    | 1    | 1  | 0 | 0 | 1 | 1            | 0 | 0      | 11/17               | STC          | Set carry                                   | 0              | 0              | 1 | 1                        | 0 | 1  | 1 | 1              | 4                              |

| CNZ                  | Call on no zero                                 | 1    | 1  | 0 | 0 | 0 | 1            | 0 | 0      | 11/17               | CMC          | Complement carry                            | 0              | 0              | 1 | 1                        | 1 | 1  | 1 | 1              | 4                              |

| CP                   | Call on positive                                | 1    | 1  | 1 | 1 | 0 | 1            | 0 | 0      | 11/17               | DAA          | Decimal adjust A                            | 0              | 0              | 1 | 0                        | 0 | 1  | 1 | 1              | 4                              |

| CM                   | Call on minus                                   | 1    | 1  | 1 | 1 | 1 | 1            | 0 | 0      | 11/17               | SHLD         | Store H & L direct                          | 0              | 0              | 1 | 0                        | 0 | 0  | 1 | 0              | 16                             |

| CPE                  | Call on parity even                             | 1    | 1  | 1 | 0 | 1 | 1            | Q | 0      | 11/17               | LHLD         | Load H & L direct                           | 0              | 0              | 1 | 0                        | 1 | 0  | 1 | 0              | 16                             |

| CPO                  | Call on parity odd                              | 1    | 1  | 1 | 0 | 0 | 1            | 0 | 0      | 11/17               | Ei           | Enable Interrupts                           | 1              | 1              | 1 | 1                        | 1 | 0  | 1 | 1              | 4                              |

| RET                  | Return .                                        | 1    | 1  | 0 | 0 | 1 | 0            | 0 | 1      | 10                  | 01           | Dissble interrupt                           | 1              | 1              | 1 | 1                        | 0 | 9  | 1 | 1              | 4                              |

|                      | Return on carry                                 | 1    | 1  | 0 | 1 | 1 | 0            | 0 | 0      | 5/11                | i una        | No-operation                                | 9              | 0              | ß | 0                        | 0 | 0  | 0 | 0              | 4                              |

| RC<br>RNC            | Return on no carry                              | 1    | i  | ŏ | i | Ö | ō            | ő | ō.     | 5/11                | NOP          | un-oberetion                                | U              | u              | v | u                        | • | •  | u | •              | •                              |

NOTES: 1. DDD or SSS - 000 B - 001 C - 010 D - 011 E - 100 H - 101 L - 110 Memory - 111 A.

<sup>2.</sup> Two possible cycle times, (5/11) indicate instruction cycles dependent on condition flags.

# Schottky Bipolar 8212

## **EIGHT-BIT INPUT/OUTPUT PORT**

- Fully Parallel 8-Bit Data Register and Buffer

- Service Request Flip-Flop for Interrupt Generation

- Low Input Load Current —

.25 mA Max.

- Three State Outputs

- Outputs Sink 15 mA

- 3.65V Output High Voltage for Direct Interface to 8080 CPU or 8008 CPU

- Asynchronous Register Clear

- Replaces Buffers, Latches and Multiplexers in Microcomputer Systems

- Reduces System Package Count

The 8212 input/output port consists of an 8-bit latch with 3-state output buffers along with control and device selection logic. Also included is a service request flip-flop for the generation and control of interrupts to the microprocessor.

The device is multimode in nature. It can be used to implement latches, gated buffers or multiplexers. Thus, all of the principal peripheral and input/output functions of a microcomputer system can be implemented with this device.

#### PIN CONFIGURATION DS. Vcc MD [ 23 INT ] oi, 00, 📮 21 DI<sub>2</sub> 20 ] 01, ا 🗀 ۵۵۵ 19 700, 8212 בום 🗀 18 ا 200 17 ءەم [ DIA DO\_ \_ ءەم 🗌 CLR STB 🔲 11 os, GND 13

#### **PIN NAMES**

| Diy-Dig | DATA IN                |

|---------|------------------------|

| DO1-DO8 | DATA OUT               |

| DS-DS2  | DEVICE SELECT          |

| MD      | MODE                   |

| STB     | STROBE                 |

| INT     | INTERRUPT (ACTIVE LOW) |

| CLR     | CLEAR (ACTIVE LOW)     |

#### **Functional Description**

#### **Data Latch**

The 8 flip-flops that make up the data latch are of a "D" type design. The output (Q) of the flip-flop will follow the data input (D) while the clock input (C) is high. Latching will occur when the clock (C) returns low.

The data latch is cleared by an asynchronous reset input (CLR). (Note: Clock (C) Overides Reset (CLR).)

#### **Output Buffer**

The outputs of the data latch (Q) are connected to 3-state, non-inverting output buffers. These buffers have a common control line (EN); this control line either enables the buffer to transmit the data from the outputs of the data latch (Q) or disables the buffer, forcing the output into a high impedance state. (3-state)

This high-impedance state allows the designer to connect the 8212 directly onto the microprocessor bi-directional data bus.

#### **Control Logic**

The 8212 has control inputs  $\overline{DS1}$ , DS2, MD and STB. These inputs are used to control device selection, data latching, output buffer state and service request flip-flop.

#### DS1, DS2 (Device Select)

These 2 inputs are used for device selection. When  $\overline{DS1}$  is low and DS2 is high ( $\overline{DS1} \cdot DS2$ ) the device is selected. In the selected state the output buffer is enabled and the service request flip-flop (SR) is asynchronously set.

#### MD (Mode)

This input is used to control the state of the output buffer and to determine the source of the clock input (C) to the data latch.

When MD is high (output mode) the output buffers are enabled and the source of clock (C) to the data latch is from the device selection logic (DS1 · DS2). When MD is low (input mode) the output buffer state is determined by the device selection logic (DS1 · DS2) and the source of clock (C) to the data latch is the STB (Strobe) input.

#### STB (Strobe)

This input is used as the clock (C) to the data latch for the input mode MD = 0) and to synchronously reset the service request flip-flop (SR).

Note that the SR flip-flop is negative edge triggered.

April, 1977

#### Service Request Flip-Flop

The (SR) flip-flop is used to generate and control interrupts in microcomputer systems. It is asynchronously set by the CLR input (active low). When the (SR) flip-flop is set it is in the non-interrupting state.

The output of the (SR) flip-flop (Q) is connected to an inverting input of a "NOR" gate. The other input to the "NOR" gate is non-inverting and is connected to the device selection logic (DS1 · DS2). The output of the "NOR" gate (INT) is active low (interrupting state) for connection to active low input priority generating circuits.

## Applications Of The 8212 -- For Microcomputer Systems

I Basic Schematic Symbol

II Gated Buffer

III Bi-Directional Bus Driver

IV Interrupting Input Port

V Interrupt Instruction Port

VI Output Port

VII 8080 Status Latch

VIII 8008 System

IX 8080 System:

8 Input Ports

8 Output Ports

8 Level Priority Interrupt

## I. Basic Schematic Symbols

Two examples of ways to draw the 8212 on system schematics—(1) the top being the detailed view showing pin numbers, and (2) the bottom being the symbolic view showing the system input or output

as a system bus (bus containing 8 parallel lines). The output to the data bus is symbolic in referencing 8 parallel lines.

#### BASIC SCHEMATIC SYMBOLS INPUT DEVICE OUTPUT DEVICE 16 18 20 22 8212 8212 (DETAILED) INT CLR CLR INT MO MΩ DS, | DS. os. 13 2 7 1 2 $v_{cc}$ GND OUTPUT INPIT FLAG STROBE SYSTEM (SYMBOLIC) 8212 8212 INPUT INT INT CLR CLR GND DATA BUS DATA BUS

#### II. Gated Buffer (3 - STATE)

The simplest use of the 8212 is that of a gated buffer. By tying the mode signal low and the strobe input high, the data latch is acting as a straight through gate. The output buffers are then enabled from the device selection logic DS1 and DS2.

When the device selection logic is false, the outputs are 3-state.

When the device selection logic is true, the input data from the system is directly transferred to the output. The input data load is 250 micro amps. The output data can sink 15 milli amps. The minimum high output is 3.65 volts.

# GATING CONTROL GND

**GATED BUFFER**

3-STATE

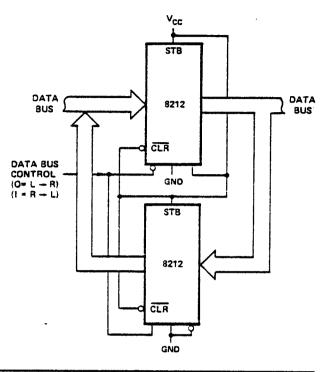

#### III. Bi-Directional Bus Driver

A pair of 8212's wired (back-to-back) can be used as a symmetrical drive, bi-directional bus driver. The devices are controlled by the data bus input control which is connected to DS1 on the first 8212 and to DS2 on the second. One device is active, and acting as a straight through buffer the other is in 3-state mode. This is a very useful circuit in small system design.

#### **BI-DIRECTIONAL BUS DRIVER**

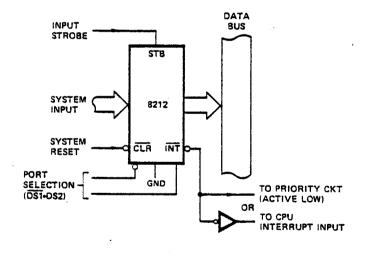

#### IV. Interrupting Input Port

This use of an 8212 is that of a system input port that accepts a strobe from the system input source, which in turn clears the service request flip-flop and interrupts the processor. The processor then goes through a service routine, identifies the port, and causes the device selection logic to go true—enabling the system input data onto the data bus.

#### INTERRUPTING INPUT PORT

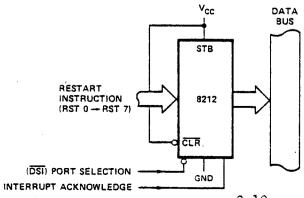

## V. Interrupt Instruction Port

The 8212 can be used to gate the interrupt instruction, normally RESTART instructions, onto the data bus. The device is enabled from the interrupt acknowledge signal from the microprocessor and from a port selection signal. This signal is normally tied to ground. (DS1 could be used to multiplex a variety of interrupt instruction ports onto a common bus).

#### INTERRUPT INSTRUCTION PORT

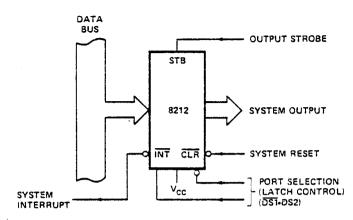

## VI. Output Port (With Hand-Shaking)

The 8212 can be used to transmit data from the data bus to a system output. The output strobe could be a hand-shaking signal such as "reception of data" from the device that the system is outputting to. It in turn, can interrupt the system signifying the reception of data. The selection of the port comes from the device selection logic. (DS1 • DS2)

#### **OUTPUT PORT (WITH HAND-SHAKING)**

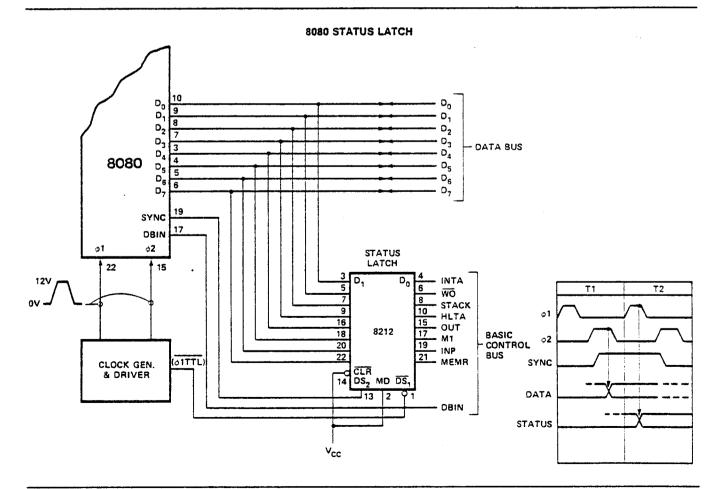

#### VII. 8080 Status Latch

Here the 8212 is used as the status latch for an 8080 microcomputer system. The input to the 8212 latch is directly from the 8080 data bus. Timing shows that when the SYNC signal is true, which is connected to the DS2 input and the phase 1 signal is true, which is a TTL level coming from the clock generator; then, the status data will be latched into the 8212.

Note: The mode signal is tied high so that the output on the latch is active and enabled all the time. It is shown that the two areas of concern are the bidirectional data bus of the microprocessor and the control bus.

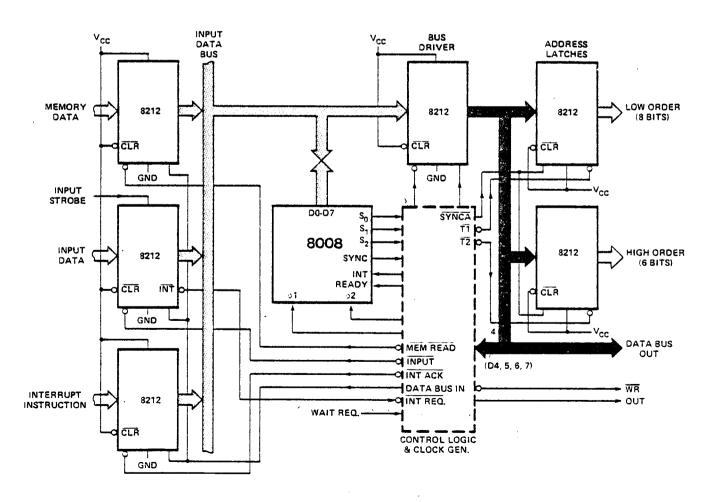

#### VIII. 8008 System

This shows the 8212 used in an 8008 microcomputer system. They are used to multiplex the data from three different sources onto the 8008 input data bus. The three sources of data are: memory data, input data, and the interrupt instruction. The 8212 is also used as the uni-directional bus driver to provide a proper drive to the address latches (both low order and high order are also 8212's) and to provide adequate drive to the output data bus. The control of these six 8212's in the 8008 system is provided by the control logic and clock generator circuits. These circuits consist of flip-flops, decoders, and gates to generate the control functions necessary for 8008 microcomputer systems. Also note that the input data port has a strobe input. This allows the proces-

sor to be interrupted from the input port directly. The control of the input bus consists of the data bus input signal, control logic, and the appropriate status signal for bus discipline whether memory read, input, or interrupt acknowledge. The combination of these four signals determines which one of these three devices will have access to the input data bus. The bus driver, which is implemented in an 8212, is also controlled by the control logic and clock generator so it can be 3-stated when necessary and also as a control transmission device to the address latches. Note: The address latches can be 3-stated for DMA purposes and they provide 15 milli amps drive, sufficient for large bus systems.

#### 8008 SYSTEM

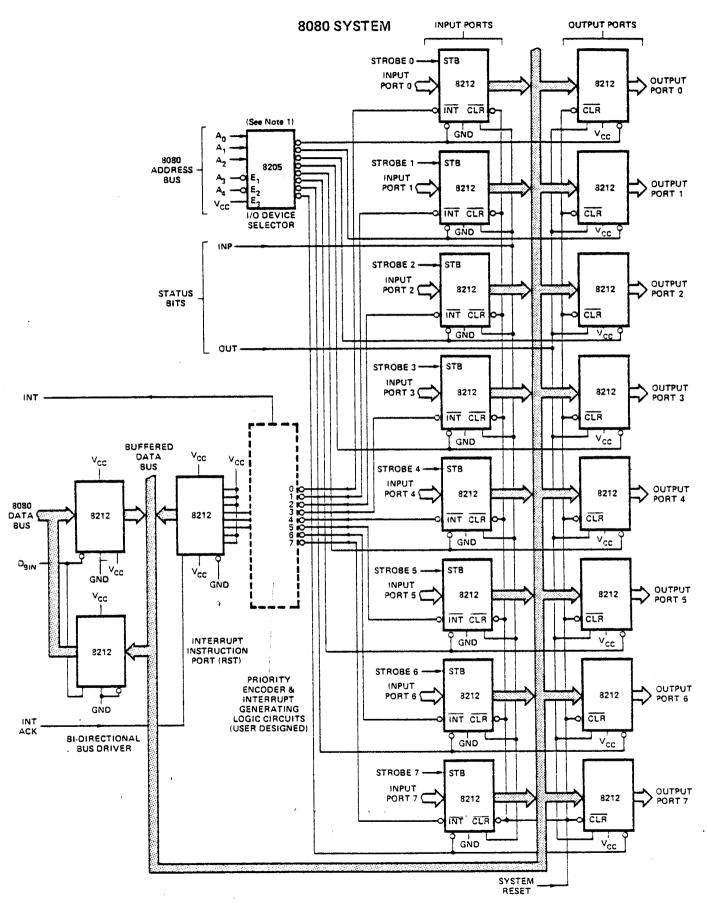

#### IX. 8080 System

This drawing shows the 8212 used in the I/O section of an 8080 microcomputer system. The system consists of 8 input ports, 8 output ports, 8 level priority systems, and a bidirectional bus driver. (The data bus within the system is darkened for emphasis). Basically, the operation would be as follows: The 8 ports, for example, could be connected to 8 keyboards, each keyboard having its own priority level. The keyboard could provide a strobe input of its own which would clear the service request flip-flop. The INT signals are connected to an 8 level priority encoding circuit. This circuit provides a positive true level to the central processor (INT) along with a three-bit code to the interrupt instruction port for the generation of RESTART instructions. Once the processor has been interrupted and it acknowledges the reception of the interrupt, the Interrupt Acknowledge signal is generated. This signal transfers data in the form of a RESTART instruction onto the buffered data bus. When the DBIN signal is true this RESTART instruction is gated into the microcomputer, in this case, the 8080 CPU. The 8080 then performs a software controlled interrupt service routine, saving the status of its current operation in the push-down stack and performing an INPUT instruction. The INPUT instruction thus sets the INP status bit, which is common to all input ports.

Also present is the address of the device on the 8080 address bus which in this system is connected to an 8205, one out of eight decoder with active low outputs. These active low outputs will enable one of the input ports, the one that interrupted the processor, to put its data onto the buffered data bus to be transmitted to the CPU when the data bus input signal is true. The processor can also output data from the 8080 data bus to the buffered data bus when the data bus input signal is false. Using the same address selection technique from the 8205 decoder and the output status bit, we can select with this system one of eight output ports to transmit the data to the system's output device structure.

Note: This basic I/O configuration for the 8080 can be expanded to 256 input devices and 256 output devices all using 8212 and, of course, the appropriate decoding.

Note that the 8080 is a 3.3-volt minimum high input requirement and that the 8212 has a 3.65-volt minimum high output providing the designer with a 350 milli volt noise margin worst case for 8080 systems when using the 8212.

Note 1. This basic I/O configuration for the 8080 can be expanded to 256 input devices and 256 output devices all using 8212 and the appropriate decoding.

## Absolute Maximum Ratings\*

\*COMMENT: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied.

#### D.C. Characteristics

$T_A = 0$ °C to +75°C  $V_{CC} = +5V \pm 5\%$

| Symbol          | Parameter                                                        |      | Limits |              | Unit | Test Conditions             |

|-----------------|------------------------------------------------------------------|------|--------|--------------|------|-----------------------------|

|                 |                                                                  | Min. | Тур.   | Max.         |      |                             |

| F               | Input Load Current<br>ACK, DS₂, CR, DI₁-DI₃ Inputs               |      |        | <b>-</b> .25 | mA   | V <sub>F</sub> = .45V       |

| F               | Input Load Current<br>MD Input                                   |      |        | <b>-</b> .75 | mA   | V <sub>F</sub> = .45V       |

| F               | Input Load Current<br>DS, Input                                  |      |        | -1.0         | mA   | V <sub>F</sub> = .45V       |

| I <sub>R</sub>  | Input Leakage Current<br>ACK, DS, CR, DI,-DI <sub>3</sub> Inputs |      |        | 10           | μΑ   | $V_R = 5.25V$               |

| R               | input Leakage Current<br>MO input                                |      |        | 30           | μΑ   | $V_{R} = 5.25V$             |

| l <sub>R</sub>  | Input Leakage Current<br>DS, Input                               |      |        | 40           | μΑ   | V <sub>2</sub> = 5.25V      |

| V <sub>C</sub>  | Input Forward Voltage Clamp                                      |      |        | -1           | V    | l <sub>c</sub> = -5 mA      |

| V <sub>IL</sub> | Input "Low" Voltage                                              |      |        | .85          | V    |                             |

| V <sub>iH</sub> | Input "High" Voltage                                             | 2.0  |        |              | V    |                             |

| V <sub>OL</sub> | Output "Low" Voltage                                             |      |        | .45          | V    | I <sub>OL</sub> = 15 mA     |

| V <sub>OH</sub> | Output "High" Voltage                                            | 3.65 | 4.0    |              | ٧    | $I_{OH} = -1 \text{ mA}$    |

| Isc             | Short Circuit Output Current                                     | -15  |        | -75          | mA   | V <sub>0</sub> = 0 V        |

| loi             | Output Leakage Current<br>High Impedance State                   |      |        | 20           | μΑ   | V <sub>0</sub> = .45V/5.25V |

| Icc             | Power Supply Current                                             |      | 90     | 130          | mA   |                             |

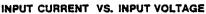

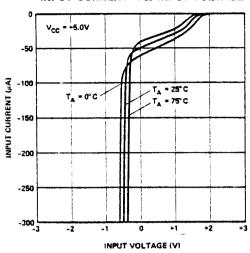

## **Typical Characteristics**

#### OUTPUT CURRENT VS. OUTPUT "LOW" VOLTAGE

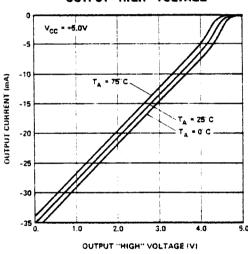

#### OUTPUT CURRENT VS. OUTPUT "HIGH" VOLTAGE

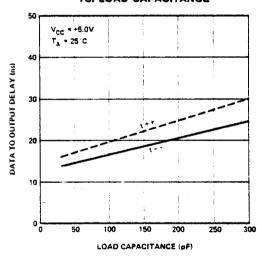

#### DATA TO OUTPUT DELAY VS. LOAD CAPACITANCE

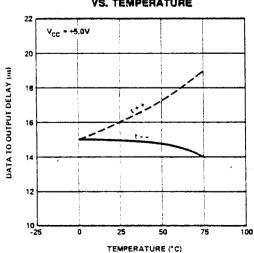

# DATA TO OUTPUT DELAY VS. TEMPERATURE

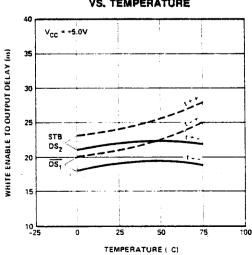

# WRITE ENABLE TO OUTPUT DELAY VS. TEMPERATURE

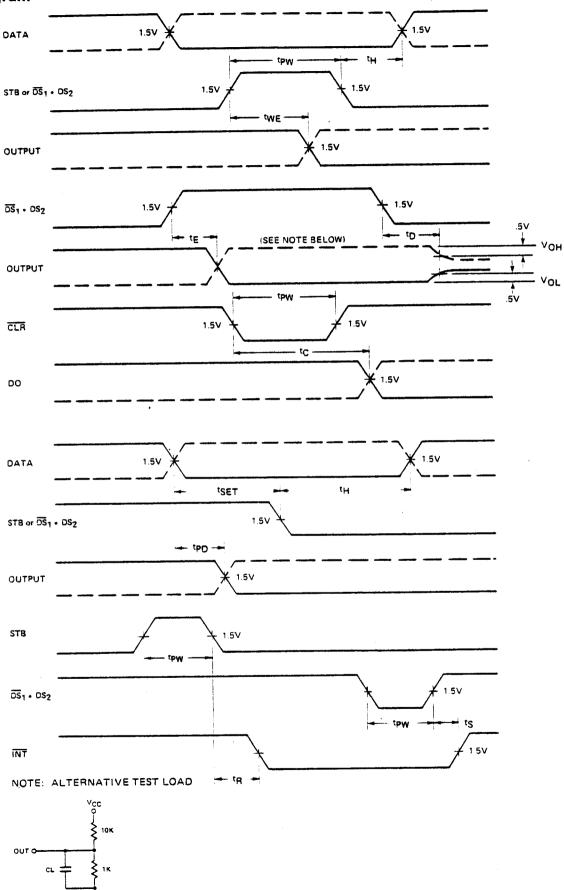

## **Timing Diagram**

## SCHOTTKY BIPOLAR 8212

## A.C. Characteristics

$T_A = 0$ °C to +75°C  $V_{CC} = +5V \pm 5\%$

| Symbol            | Parameter                    | Limits         |                                                  |      | 11-24 | T               |

|-------------------|------------------------------|----------------|--------------------------------------------------|------|-------|-----------------|

|                   |                              | Min.           | Тур.                                             | Max. | Unit  | Test Conditions |

| t <sub>pw</sub>   | Pulse Width                  | 30             |                                                  |      | ns    |                 |

| t <sub>pa</sub>   | Data To Output Delay         | - <del> </del> |                                                  | 30   | ns    |                 |

| t <sub>we</sub>   | Write Enable To Output Delay |                | <del>*************************************</del> | 40   | ns    |                 |

| t <sub>sa</sub> , | Data Setup Time              | 15             |                                                  |      | ns    |                 |

| th                | Data Hold Time               | 20             |                                                  |      | ns    |                 |

| t.                | Reset To Output Delay        |                |                                                  | 40   | ns    |                 |

| t,                | Set To Output Delay          |                |                                                  | 30   | ns    |                 |

| e e               | Output Enable/Disable Time   |                |                                                  | 45   | ns    |                 |

| t <sub>c</sub>    | Clear To Output Delay        |                |                                                  | 55   | ns    |                 |

CAPACITANCE F = 1 MHz  $V_{81AS}$  = 2.5V  $V_{CC}$  = +5V  $T_A$  = 25°C

| Symbol          | Test                                       | LIN  | LIMITS |  |  |

|-----------------|--------------------------------------------|------|--------|--|--|

|                 |                                            | Тур. | Max.   |  |  |

| C <sub>tN</sub> | DS, MD Input Capacitance                   | 9 pF | 12 pF  |  |  |